stefanovi - Fotolia

Neue Memory-Technologien treten gegen NAND-Flash an

NAND Flash Memory hat viele Innovationen und Änderungen erfahren, darunter besonders 3D-NAND und 3D XPoint. Doch weitere Alternativen stehen schon seit einiger Zeit am Start.

Flash Memory wurde sehr schnell bekannt, als Intel 1988 die ersten NOR-Chips herausbrachte. NOR (von engl. „not or“ = „nicht oder“) bereitete drei Jahre später den Weg fūr NAND Flash. NAND (von engl. „not and“ = „nicht und“) fand die schnellste Verbreitung in der bisherigen Geschichte der Halbleitertechnik, in zehn Jahren von 1,8 Milliarden verkauften Stück bis zu 18 Milliarden. Und im Jahr 2017 erzielte man mit dieser Technologie einen Rekordumsatz von 50 Milliarden Dollar, was dem weltweiten Halbleitermarkt von 1990 entspricht. Bei NAND Flash handelt es sich ganz eindeutig um Big Business.

Aber es stehen Änderungen an, da die Hersteller mehrere neue Technologien als mögliche Alternativen entwickeln.

NAND Flash stösst an seine Grenzen

Während der letzten 40 Jahre verdoppelte sich die Anzahl der Transistoren auf einem Halbleiter-Chip dank dem Mooreschen Gesetz alle ein oder zwei Jahre, wobei sich die Größe eines einzigen Bits durchschnittlich um 30 Prozent pro Jahr reduzierte. Dies führte wieder zu Kostensenkungen und größerer Verbreitung der Chips. Diese Reduzierungen um 30 Prozent werden als „Process Shrinks“ bezeichnet, und das andauernde Phänomen der konstanten Verringerung von Größe und Kosten ist unter dem Namen „Scaling“ bekannt.

Kontinuierliche Reduzierungen gelten für die meisten Halbleiter, aber bei Flash Memory gibt es ein besonderes Problem: Bei Flash werden die Bits auf einem Floating Gate als Elektronen gespeichert, und die Anzahl der Elektronen, die ein Floating Gate aufnehmen kann, ist proportional zu der Größe des Transistors. Bei einer Fläche von 15 Nanometern (nm) beträgt der Unterschied zwischen einer Eins und einer Null nur ein paar Dutzend Elektronen – eine extrem schwierige Größe angesichts der Struktur eines digitalen Chips. Würden die Hersteller die Chipgröße um weitere 30 Prozent reduzieren, so wie es immer getan haben, würde die Anzahl der Elektronen unter ein noch wahrnehmbares Niveau fallen.

Der gesamte Halbleitermarkt stützt sich auf die Erwartung, dass die Reduzierungen bei den Kosten weitergehen werden. Und es wird nicht erwartet, dass die Preissenkungen bei Flash plötzlich zu Ende gehen würden. Aber was könnte trotz der technischen Beschränkungen bei ebenflächigem NAND getan werden?

3D-NAND als Rettung

Toshiba kam 2006 mit einer cleveren Lösung heraus. Statt weiter damit fortzufahren, die Transistoren auf einem Chip zu verkleinern, besann man sich auf eine vertikale Struktur und baute Transistoren nach oben – ähnlich wie bei den vertikalen Gärten an den Außenmauern von manchen städtischen Bürogebäuden.

Mit diesem Ansatz, die Anzahl der Transistoren auf einem Chip zu vergrößern, wollte Toshiba auch dann die Kosten von Flash-Bits weiter verringern, wenn eine Reduzierung bei den Transistoren nicht mehr möglich war. Dieser Ansatz wurde Bit Cost Scaling oder BiCS genannt und wurde zur Grundlage von 3D-NAND Flash.

BiCS erlaubt nicht nur die Fortsetzung der Kostensenkungen, es unterstützt auch weiterhin den Einsatz von NAND Flash, da 3D-NAND und klassisches NAND ähnlich genug sind, um abwechselnd und mit wenig oder gar keinem Re-Design benutzt zu werden. So wird ein Endanwender zwei USB-Flashdrives, eines mit 3D-NAND und eines mit ebenflächigem NAND, einsetzen können und keine Unterschiede feststellen. Dies ist ein eindeutiger Vorteil gegenüber einigen anderen neuen Memory-Technologien.

Die Industrie übernahm den Ansatz von Toshiba. Mit BiCS werden Bits in einer Säule übereinander angeordnet, die aus mehreren Halbleiterschichten besteht. Es stellte sich dann die Frage, wie hoch kann man diese vertikalen Bit-Türme in einem Hohlraum aufeinander schichten? Das Problem ist noch nicht geklärt.

Als Toshiba zuerst BiCS entwickelte, war man davon ausgegangen, dass die Anzahl der Bits durch die Schichten im Chip und durch die Dimensionen des Hohlraums, der die Säule bildet, begrenzt sein würde. Die Hersteller können diesen Hohlraum nicht kleiner als etwa 20 nm machen, weil ein paar konzentrische Materialschichten mit einer minimalen Dicke die Außenwand bilden. Die Tiefe der Säule ist andererseits proportional zu der Anzahl der vertikalen Schichten, die ebenfalls über eine minimale Dicke verfügen. Wegen dieser Beschränkungen ist der Formfaktor des Hohlraums – die Tiefe geteilt durch den Durchmesser – durch die Anzahl der vertikalen Layer im Flash bestimmt.

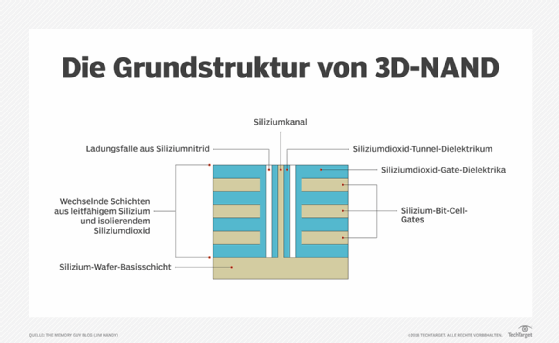

3D-NAND bauen

3D-NAND nutzt einen relativ einfachen Ansatz, um mehr Transistoren auf einen Chip zu packen: Sie werden seitwärts eingebaut, ganz im Gegensatz dazu, wie Halbleiter immer gebaut worden waren.

Die meisten Chips werden in einem photolithographischen Prozess hergestellt. Die erforderlichen Muster, um Milliarden von Transistoren auf einen Chip zu bringen, werden auf die Oberfläche eines Silicon Wafer projiziert, indem Licht durch eine so genannte „Maske“ geleitet wird, die einem photographischen Negativ ähnelt, um anschließend die unbelichteten Teile in Silikon abzubilden. Dies ist seiner Natur nach ein ebenflächiges Verfahren, Photographien sind dagegen immer zweidimensional.

Doch wie wird dieser Vorgang in 3D umgewandelt? Die Erfinder von 3D erkannten, dass bestimmte, sich wiederholende Muster ihres Plans auf andere Weise erzeugt werden konnten. Wenn man mehrere Materialschichten auf der Oberfläche des Chips anbringen würde, könnte man anschließend Löcher für Hohlräume durch alle Schichten durchstoßen. Dies würde zu einer Struktur führen, die einer Photographie ähnelt, die seitwärts an der Wand der Löcher angebracht wäre. Und dies kann wegen der sich abwechselnden Schichten ohne einen photographischen Prozess geschehen – die Muster sind bereits in den verschiedenen Schichten enthalten.

Natürlich gibt es noch weitere technische Feinheiten, aber so sieht der wesentliche Kern von 3D-NAND aus.

Formfaktoren von 40:1 sind schwierig herzustellen, und 60:1 stellt extreme Anforderungen an den Herstellungsprozess. Aber wenn die Anzahl der Schichten zunimmt, ist ein höherer Formfaktor erforderlich. Damit schien 3D-NAND auf drei Generationen oder etwa 100 Schichten beschränkt zu sein, bevor man zu einer neuen Technologie übergehen würde.

Forscher auf dem Feld von Halbleitern sind jedoch bewundernswert innovativ und sie haben sich bereits eine neue Idee mit der Bezeichnung „String Stacking“ ausgedacht, um eine deutlich höhere Anzahl von Schichten zu unterstützen. Mit String Stacking lässt sich eine bestimmte Anzahl von 3D-NAND-Layern erzeugen und dann wird oberhalb von ihr eine andere Schichtgruppe (set of layers) errichtet. Mit jedem neuen Layer Set wird ein neuer Hohlraum gebildet, aber dieser Hohlraum geht durch eine kleinere Anzahl von Schichten hindurch, so dass ihr Formfaktor bescheiden bleibt. Zum Beispiel erzeugt Micron Technology zweimal eine 32-Layergruppe, um sein aktuelles Produkt von 64-Layer-3D-NAND fertigzustellen, anstatt einen einzigen Hohlraum durch 64 Layer zu schaffen. So summieren sich zwei 30:1-Formfaktoren anstatt einem einzigen von 60:1.

Niemand weiß genau, wie viele Strings sich aufeinander stapeln lassen, bevor eine physische Grenze erreicht wird. Die gegenwärtig vorherrschende Ansicht geht von einer Grenze bei 500 Layern aus. Allerdings hat sich in der Welt der Halbleiter schon oft herausgestellt, dass allgemeine Weisheiten falsch waren.

Die 64-Layer-Chips von heute verfügen über eine Dichte in einer Höhe von einem Terabit (128 GByte), so dass ein 500-Layer-Chip vermutlich fast zehnmal so viel Daten speichern kann. 1-Terabyte-Chips sind sicher vorstellbar. Wenn ein 1-Terabyte-Chip auf einer Basis von 500-Layer-Prozessen gebaut würde, wäre er nicht größer als sein 128-Gigabyte-Gegenstück mit 64 Layern von heute.

Die klare Auswirkung von String Stacking bedeutet, dass uns 3D-NAND für lange Zeit erhalten bleibt.

Und was ist mit 3D XPoint?

Im Jahr 2015 kūndigten Intel und Micron eine neue Art von Memory mit Namen 3D XPoint (gesprochen Crosspoint) an. Diese Technologie versprach dynamische RAM-ähnliche Geschwindigkeiten zu einem Preis, der zwischen DRAM und NAND Flash liegen sollte. Das Ziel besteht darin, einen neuen Memory-Layer zwischen DRAM Main Memory und NAND-SSDs zu lancieren, um das Preis-Leistungs-Verhältnis von Computern zu verbessern.

3D XPoint sollte nicht NAND Flash oder DRAM ersetzen, obwohl es wahrscheinlich dazu benutzt wird, die Menge an DRAM für verschiedene Performance-Levels zu reduzieren. Dies stellt eine große Änderung gegenüber neuen Memory-Technologien dar, die bereit sind, Flash oder DRAM zu ersetzen, sobald eine von ihnen an ihre Grenzen gestoßen ist.

Bisher war 3D XPoint nur in einer Schnittstelle für PCIe Non-Volative Memory Express (NVMe) verfügbar. Obwohl NVMe die schnellste Schnittstelle für SSDs ist, ist es im Vergleich zu der naturgemäßen Geschwindigkeit von 3D XPoint Memory langsam. Es ist in der Tat so langsam, dass die aktuellen Optane SSDs von Intel nur sechs- bis achtmal so schnell sind wie ihre Pendants mit NAND Flash, obwohl Intel und Micron erklären, dass 3D XPoint 1.000 mal schneller als NAND Flash wäre.

Sicher ist ein DIMM-Interface notwendig, um die DRAM-ähnliche Geschwindigkeit von 3D XPoint freizusetzen und seine Kosten-Performance-Vorteile einzukassieren. Intel hat versprochen, 3D XPoint Memory in einem DIMM-Format auszuliefern, aber bis jetzt scheint es bei solchen öffentlichen Ankündigungen geblieben zu sein. Bei Intel sagt man andererseits, man hätte diese DIMMs bereits an Google während des Flash Memory Summit im August 2018 ausgeliefert.

In einem Report von Objective Analysis aus dem Jahr 2015 wurde der wohl wahrscheinlichste Markt für 3D XPoint Memory im Bereich DIMMs für Server gesehen. Wir halten das nach wie vor für sehr wahrscheinlich. Der aktuelle Markt für 3D XPoint ist relativ winzig und spricht hauptsächlich Gamer an, die bereit sind, viel Geld für marginale Performance-Verbesserungen auszugeben.

Die Strategie von Intel für 3D XPoint

Zum Nachteil von Intel ist der Markt für 3D XPoint so klein, dass sich keine hohen Stückzahlen für entsprechende Produkte ergeben. Aber ohne große Volumina werden die Produktionskosten hoch bleiben, wahrscheinlich sogar höher als die von DRAM. Doch Intel muss 3D XPoint Memory zu einem niedrigeren Preis als DRAM verkaufen, um es für Endkonsumenten attraktiv zu machen. Dies bedeutet, Intel muss Verluste einstecken, um einen neuen Markt zu etablieren.

Ein solcher Ansatz würde sich wahrscheinlich nicht für andere Hersteller lohnen, aber bei Intel verhält sich die Sache anders. 3D XPoint Memory versetzt das Unternehmen in die Lage, teurere Prozessoren zu verkaufen und so das Geld zurückzuholen, das man bei dem Verkauf von 3D XPoint verliert.

Weitere neue Memory-Technologien

3D XPoint ist nur eine aus einer Reihe von neuen Memory-Technologien, die wir untersucht haben. Einige befinden sich schon seit einer beträchtlichen Zeit in Entwicklung wie zum Beispiel Phase-Change Memory (PCM), über das Gordon Moore von Intel schon 1970, vor fast 50 Jahren, als Co-Autor einen Artikel verfasst hat.

Diese Technologien versprechen hohe Performance, niedrigen Energieverbrauch, Langlebigkeit und – am wichtigsten – die Fähigkeit, über die Erweiterungsgrenzen von DRAM und NAND Flash hinauszugehen. Aber die Entwickler von NAND Flash und DRAM haben bisher noch immer Lösungen für dieses Problem gefunden: 3D-NAND ist ein großes Beispiel dafür. Und sie haben damit die Realisierungschancen von alternativen, neueren Technologien, die NAND und DRAM ersetzen könnten, weiter hinausgeschoben.

Der Markt für Embedded Memory wird höchstwahrscheinlich noch die eine oder andere dieser neuen Technologien hervorbringen. Aber es wird wohl eine lange Zeit dauern, bis eine dieser Technologien die Gelegenheit bekommt, DRAM oder NAND Flash zu ersetzen. Die Produkte für Embedded Memory werden eine neue Technologie eher übernehmen, weil Memory auf einem Logic Chip einfach und günstig zu installieren sein muss – entsprechend den Herstellungsprozessen von ASICs, Mikrocontrollern und Mikroprozessoren.

NOR Flash, der am meisten verbreitete nicht-flüchtige Speicher auf solchen Chips, hat Schwierigkeiten, über 45 nm hinauszugehen, obwohl es bereits Labor-Prototypen gibt, die Prozesse mit 14 nm einsetzen. In ähnlicher Weise ist statischer RAM problematisch, da die Größe eines SRAM-Bits nicht im Verhältnis zum Prozess skaliert. Dies kann dazu führen, dass der SRAM-Anteil des Chips aufgebläht wird und dass die Kostenvorteile begrenzt bleiben, die durch Reduzierungen bei ASICs, Mikrocontrollern und Mikroprozessoren erzielt werden könnten.

Sowohl NOR als auch SRAM sind Kandidaten für einen Ersatz durch neue Memory-Technologien. Im Folgenden eine kleine Übersicht solcher Alternativen:

Magnetic RAM (MRAM) stützt sich auf magnetische Technologien, die bereits in großen Mengen für die Schreib- und Leseköpfe in Festplatten produziert werden. Everspin Technologies produziert diese nicht-flüchtige Technologie seit fünf Jahren als Stand-alone Memory, und eine embedded Version wird für alle führenden Hersteller entwickelt. MRAM basiert auf einer DRAM-ähnlichen Zelle mit einem Transistor, wodurch es bei den Kosten mit DRAM konkurrieren kann, aber nicht mit NAND Flash.

Phase-Change Memory ist die Grundlage für 3D XPoint Memory von Intel und Micron. Es ging vor etwa einem Jahrzehnt als Ersatz für NOR Flash in Produktion, wurde aber nur von Intel, Samsung und STMicroelectronics unterstützt. Alle drei Hersteller haben sich aber bald wieder zurückgezogen.

Ferroelectric RAM (FRAM) wurde schon seit mehr als 20 Jahren produziert, fand aber nur wenig Akzeptanz, weil bleihaltige Materialien verwendet wurden, die sich negativ auf das verwendete Silicon auswirkten. Trotz dieses Sachverhalts hat Fujitsu mehr FRAM-basierte Chips produziert als wahrscheinlich alle anderen alternativen Memory-Angebote zusammen. Neue Forschungen haben ein besser geeignetes Basismaterial zu Tage gefördert – „hafnium oxide“ –, das sich als Ferroelectric Layer eignet und das Interesse an dieser Alternative wieder steigern dürfte.

Conductive-bridging RAM (CBRAM) basiert auf der Verbindung von Metallfasern mit kupferhaltigem Glas. Adesto Technology ist das einzige Unternehmen, das diesen Memory-Typ verkauft.

Resistive RAM (ReRAM) von Crossbar arbeitet mit einer in etwa ähnlichen Technologie, bei der Nanometall-Fasern mit einer kupferhaltigen Glasschicht verbunden werden. ReRAM hat eine Art von Bit-Zelle mit internem Schaltmechanismus entwickelt, der den Produktionsprozess vereinfacht, da ein externer Schalter entfällt.

Oxygen depletion RAM (OxRAM) funktioniert ähnlich wie CBRAM, während Sauerstoff-Ionen von einem kupferhaltigen Glas entfernt werden, um einen direkten Pfad zu bilden. Doch die Technologie befindet sich noch nicht in Produktion. Hewlett Packard Enterprise (HPE) plante bis vor einem Jahr, OxRAM in seinem fortschrittlichen Computermodell The Machine einzusetzen, aber dieser Ansatz mit Namen Memristor wurde immer wieder verschoben.

Nanotube RAM oder NRAM von Nantero beruht auf einem Layer von Kohlenstoffnanoröhrchen, die elektrisch zusammengepresst oder erweitert werden können, um einen hohen oder niedrigen Widerstand zu erzeugen.

Mit der Ausnahme von MRAM beruhen alle diese Technologien auf einem zweipoligen Schalter. Diese Schalter unterstützen eine winzige Bit-Zellengröße von -4f2 oder das Vierfache des kleinsten optischen Features auf dem Chip. Sie können auch übereinander gestellt werden, ähnlich wie bei 3D XPoint Memory, um Kosten einzusparen.

Bis zur jüngsten Entdeckung, dass man Hafnium Oxide für die Herstellung von FRAM verwenden kann, erforderten alle oben genannten Technologien den Einsatz von neuen Materialien, über die man nicht so genau Bescheid wusste wie über das zugrunde liegende Silicon. Dies stand natürlich ihrer Anwendung im Weg, da diese neuen Materialien ihrem Einsatz in der Massenproduktion Schwierigkeiten bereiteten.

Die Kosten sind der bedeutendste Faktor, warum diese Technologien noch nicht die bestehenden Memory-Lösungen ersetzen können. Alle sind sehr viel teurer als DRAM oder NAND Flash. Deshalb kommt es nicht dazu, dass sie außer in einigen Nischenbereichen eingesetzt werden, bei denen ein paar technische Features ihre höheren Kosten rechtfertigen. Was FRAM angeht, ist die schnelle Schreibfunktion bei niedrigem Energieverbrauch attraktiv. Bei MRAM spielen die schnelle Schreibfunktion und die Nichtflüchtigkeit des Speichers ohne die Notwendigkeit, einen unzuverlässigen Akku einzusetzen, eine Rolle. PCM wurde wegen seiner hohen Strahlungstoleranz bei Satelliten eingesetzt, und CBRAM ist aus ähnlichen Gründen bei chirurgischen Instrumenten und den hohen Dosen von Röntgenstrahlen ausgewählt worden.

Solange keine dieser Technologien ein genügend hohes Produktionsvolumen erzielt, werden auch die Produktionskosten nicht niedrig genug sein, um irgendeine der etablierten Memory-Technologien ersetzen zu können. Sie werden nicht in großen Mengen produziert werden, solange der Markt dafür nicht da ist, und der Markt wird sich nicht entwickeln, solange die Preise nicht heruntergehen. Es ist die typische Huhn-und-Ei-Problematik.

Was im nächsten Jahrzehnt zu erwarten ist

NAND Flash wird noch ein weiteres Jahrzehnt lang eine Rolle spielen, gefolgt von DRAM. Wenn Intel seine Ziele für 3D XPoint umsetzen kann, dann wird es auch zu großen Absatzzahlen vorstoßen – obwohl es wahrscheinlich diese Technologie erst mal mit Verlusten verkaufen muss, um überhaupt zu diesem Punkt zu gelangen. Die anderen neuen Memory-Technologien werden in der näheren Zukunft bei On-Chip-Memories Erfolg haben, aber sich wahrscheinlich noch für eine Weile nicht gegen alleinstehende DRAM- und NAND-Flash-Chips durchsetzen.